The SDN-Switch OpenFlow 1.4 Series

The SDN-Switch OpenFlow 1.4 Series combines ultra-low latency Layer 1 switching with programmable FPGA technology. The series contains:

• The SDN-Switch OpenFlow 1.4 Connect Layer 1+ network devices with port-to-port latencies as low as 4 nanoseconds.

• The FPGA-enabled SDN-Switch OpenFlow 1.4 E & L Series which are programmable switches that can host up to 3 FPGAs and can be leveraged to run Acronics Solutions’s network applications.

• The SDN-Switch OpenFlow 1.4 network applications which feature capabilities for ultra-low latency multiplexing in as low as 39 nanoseconds (MetaMux), tapping, tap aggregation, and sub-nanosecond precise timestamping (MetaWatch) and low-latency connectionsharing with enhanced security & privacy (MultiAccess). Acronics Solutions also provides development toolkits & IP Cores for users to develop their own applications.

|

Layer 1+ switching devices

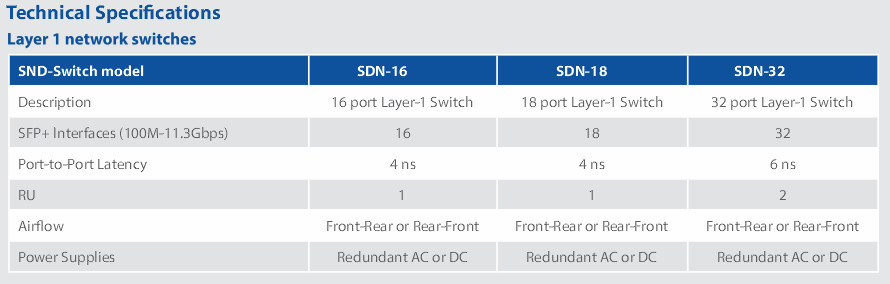

SDN-Switch OpenFlow 1.4 Connect Series Layer 1+

switches are powerful network devices designed for ultra-low latency of just 4 nanoseconds. Available in 16, 18 or 32port device options, they combine a multitude of network functionality on a single device:

• Signal regeneration

• Media conversion

• Port mirroring

• Telemetry

• Dynamic patching/link management

• Layer 1+ statistics on every link

All network devices are deterministic with virtually undetectable jitter as they neither buffer or queue data, hence utilizing 100% of available bandwidth. The SDN-Switch OpenFlow 1.4 Connect Series platform is packet-aware providing comprehensive packet statistics, signal quality monitoring including eye diagrams, and diagnostics. Packet replication provides the ability to sniff packets without affecting the data path.

|

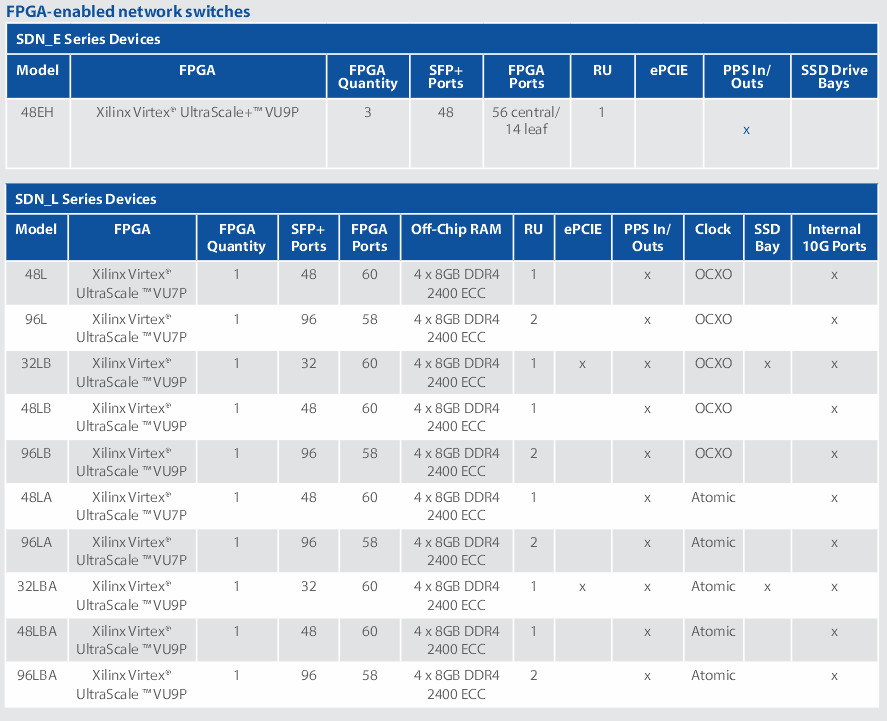

FPGA-enabled devices

SDN-Switch OpenFlow 1.4 E & L Series devices leverage the latest FPGA technology to allow companies to develop and deploy cutting-edge network applications. Available in 32, 48 or 96 SFP+ port options, the FPGA-enabled switches include a host of functionality:

• Up to 3 FPGAs on a single device

• 5 ns layer 1 switching between network

• 3 ns latency from front panel to FPGA

• Various specifications for RAM, buffers, and transceivers

• Extensive development toolkits and low-latency IP Cores

All FPGA-enabled devices are optimized for Acronics Solutions’s high performance network applications and can equally be leveraged torun 3rd party partner applications. FPGA application developers can utilize the platform to deploy and deliver their performance critical apps. In addition to the market-leading FPGA functionality, the devices offer all of the Layer 1+

|

The MOS operating system

MOS provides a core set of features that are common across the SDN-Switch OpenFlow 1.4 platform. It is based on Linux and provides a command line and web interface as well as support for other management protocols. MOS provides a standard, mature and powerful platform with the commands, tools and packages such as syslog, net-snmp, daemons, RPMs, Bash, Python, authentication, and security.

• Various specifications for RAM, buffers, and transceivers

• Extensive development toolkits and low-latency IP Cores

All FPGA-enabled devices are optimized for Acronics Solutions’s high performance network applications and can equally be leveraged torun 3rd party partner applications. FPGA application developers can utilize the platform to deploy and deliver their performance critical apps. In addition to the market-leading FPGA functionality, the devices offer all of the Layer 1+ network functionality also found on the Connect series.

Acronics Solutions offers several powerful network applications to simplify and transform network infrastructure. These applications are designed for use cases including ultra-low latency exchange trading, network visibility and providing vendor or brokerbased shared services. Network applications are supported on the SDN-Switch OpenFlow 1.4 Series of systems

| Application | Key Features | Use it for.. |

|

MetaWatch

Advanced network

monitoring

|

• Tapping

• Large scale, lossless tap aggregation

• Multi-port data capture

• Sub-nanosecond precise time stamping

• Deep buffering (32 GB)

|

• In-depth network monitoring and visibility

• Improved network reliability & troubleshooting

problems

• Market data & packet capture

• Accurate latency measurement & monitoring

• Regulatory compliance (MiFID II - RTS 25)

|

|

MetaMux

Low-latency multiplexing

|

• Data aggregation in 39 nanoseconds

• Deterministic jitter

• Packet statistics

• BGP & PIM support

|

• Ultra-low latency network connectivity for trading

• Market data fan-out and data aggregation for

order entry at nanosecond levels

|

|

MultiAccess

Connection sharing with

enhanced security

|

• Low-latency multiplexing and security

• ACL-based configurable filtering

• Easy to deploy data privacy for

connection sharing

• Simplified footprint for both mux and

filtering applications

|

• Secure network connection sharing

• Providing sponsored access to multiple clients

• Multi tenant exchange access

• Low latency interconnect sharing

|

IP Cores and Development Toolkits

Acronnics Solutions provides a built-in application framework allowing developers to wrap applications into simple packages for deployment; streamlining operational processes. Acronics Solutions development toolkits enable complete and unfettered access to the facilities provided by the in-system FPGAs. The MOSAPI provides monitoring, CLI, API, FPGA image management, and other facilities to allow application developers to concentrate on the core application functionality. These are the same APIs and developer kits used by the Acronics Solutions engineering team to develop and deploy our applications.

Acronics Solutions develops FPGA applications based on a mature base of network logic IP. To make it easier to develop compelling FPGA based network applications, Acronics Solutions licenses that IP as IP cores for use on the SDN-Switch OpenFlow 1.4 platform. These are supported, proven building blocks that reduces time to implement your applications.

| Core | Overview | Use it for... |

|

10G MAC-PHY

IP Core

|

An IP core for interfacing 10 gigabit Ethernet with low latency.

• Implements a low latency Ethernet MAC and Physical layer (10GBASE-R)

• Connects directly to FPGA top level serial transceiver pins and provides

separate AXI4 interfaces for RX and TX user data

• Supports Xilinx Virtex® 7, Xilinx Kintex® UltraScale™, and Virtex®

• UltraScale+™ FPGA’s

|

• Accelerating your own applications

access to the 10G network

|

|

Mux

IP Core

|

Implements the same functionality as the Acronics Solutions MetaMux

application.

• allows for customizable radix and number of multiplexing cores

• e.g. one 4:1, plus a 13:1, plus a 14:1, etc

|

• Sharing the FPGA between the mux

functionality and your own application

• Building a multiplexing app with

different configurations than the

standard MetaMux application.

|

|

MMP

IP Core

|

Provides a bus that leverages parallel I/O between FPGA’s on the

SDN triple FPGA platforms

• 8 ns intra FPGA latency

• Provides a low latency clock domain crossing FIFO

• Supports four MMP links connecting each Leaf FPGA to the Central

FPGA and two MMP links connecting the two Leaf FPGAs together

|

• The lowest latency, parallel

communications bus for your multi

FPGA applications

• The fastest way to involve two

FPGAs in a trading decision such as

“splitting risk logic from trading

logic”

|

- @ Copyright 2020 Acronics